# MIC2596/2597

**Dual Channel Negative Voltage Hot Swap Controllers**

#### Advance Information

## **General Description**

The MIC2596 and MIC2597 are dual channel negative voltage hot swap controllers designed to facilitate safe PC board insertion into and removal from live backplanes. To minimize external components, each channel of the MIC2596/MIC2597 has an integrated high voltage power MOSFET. Built-in current sensing in each channel provides inrush current limiting, by regulating the channel's output current to a usersettable maximum. Current sensing also provides programmable overcurrent and open-load detection. A channel will be turned off if it experiences overload or no-load conditions lasting longer than programmable intervals. Foldback current limiting holds power dissipation of the internal MOSFETs at safe levels during overloads, and very fast shutdown response to faults ensures protection for both system power supplies and the load. The MIC2596 will automatically attempt to restart into an overcurrent fault until the fault is cleared, while the MIC2597 will latch the output in the off state until it is reset by external action. A logic-compatible signal is provided on each channel to indicate overcurrent or undercurrent fault conditions.

## Features

- Allows safe hot-swap in -48V systems

- Operates to -70V

- Programmable inrush current limiting

- Two thermally isolated channels

- Overcurrent fault sensing and protection

- Nuisance trip prevention circuitry

- Open-load detection

- Logic compatible Enable and Fault signals

- Separate analog and logic ground pins support large system ground differentials (±8V)

#### Applications

- Central Office Switching

- -48V Power Distribution

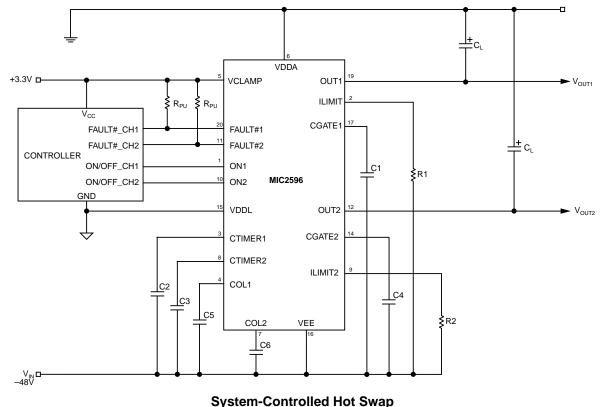

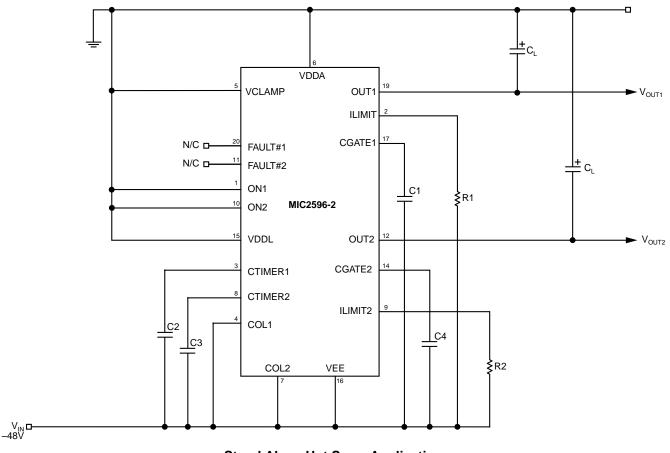

## Typical Application

Micrel, Inc. • 1849 Fortune Drive • San Jose, CA 95131 • USA • tel + 1 (408) 944-0800 • fax + 1 (408) 944-0970 • http://www.micrel.com

## **Ordering Information**

| Part Number   | ON Signal   | <b>Circuit Breaker Function</b> | Package                     |

|---------------|-------------|---------------------------------|-----------------------------|

| MIC2596-1BTS  | Active-High | Auto-Retry                      | 20 pin TSSOP                |

| MIC2596-2BTS  | Active-Low  | Auto-Retry                      | 20 pin TSSOP                |

| MIC2597-1BTS  | Active-High | Latched Off                     | 20 pin TSSOP                |

| MIC2597-2BTS  | Active-Low  | Latched Off                     | 20 pin TSSOP                |

| MIC2596-1BTSE | Active-High | Auto-Retry                      | 20 pin Exposed Pad<br>TSSOP |

| MIC2596-2BTSE | Active-Low  | Auto-Retry                      | 20 pin Exposed Pad<br>TSSOP |

| MIC2597-1BTSE | Active-High | Latched Off                     | 20 pin Exposed Pad<br>TSSOP |

| MIC2597-2BTSE | Active-Low  | Latched Off                     | 20 pin Exposed Pad<br>TSSOP |

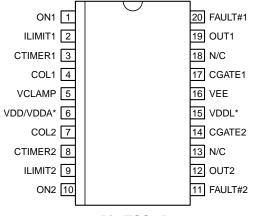

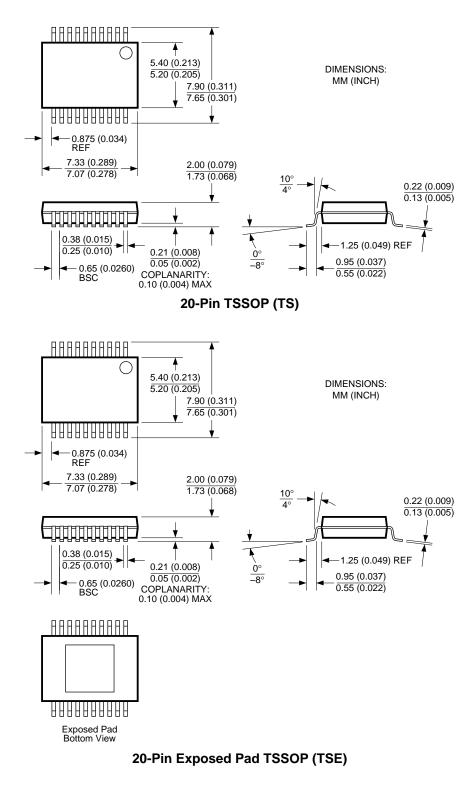

#### 20-Pin TSSOP

## **Pin Descriptions**

| Pin Number | Pin Name        | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 20, 11     | FAULT1#/FAULT2# | Fault Status Output, Active-low - Asserted when the circuit breaker trips upon overcurrent, open-load or thermal shutdown conditions.                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| 1, 10      | ON1/ON2         | Enable Input - Active-high (MIC259x-1) or active-low (MIC259x-2). When asserted ON will initiate a start cycle by activating the GATE output. Tog-<br>gling ONx will also reset the circuit breaker in the MIC2597.                                                                                                                                                                                                                          |  |  |  |  |

| 3, 8       | CTIMER1/CTIMER2 | Current Limit Response Timer. A capacitor connected to this pin defines the period of time $t_{FLT}$ in which an overcurrent event must last to signal a fault condition and turn the output off.                                                                                                                                                                                                                                            |  |  |  |  |

| 16         | V <sub>EE</sub> | Negative Supply Voltage Input.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 2, 9       | ILIMIT1/ILIMIT2 | Current Limit Set. The current limit threshold is set by connecting a resistor between this pin and $V_{EE}$ . When the current limit threshold of a channel is exceeded for $t_{FLT}$ the circuit breaker for that channel is tripped and its respective output is immediately shut off.                                                                                                                                                    |  |  |  |  |

| 19, 12     | OUT1/OUT2       | Switch Outputs. Connect to load.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 6          | VDDA            | Positive Supply Input. Normally connected as the power ground reference negative supply (–48V) systems. V <sub>DDA</sub> is the IC's "analog ground," used fo internal biasing relative to –V <sub>EE</sub> .                                                                                                                                                                                                                                |  |  |  |  |

| 5          | VCLAMP          | FAULT# Clamp Voltage. A small bias current into this pin (usually supplied by the controlling logic's supply voltage) powers internal circuitry which establishes the active low voltage of the FAULT# signals. In normal circuit configurations, the low-level output voltage will be clamped to V <sub>DDL</sub> .                                                                                                                         |  |  |  |  |

| 4, 7       | COL1/COL2       | Open-Load Detect Timer - When the load current falls below 8% of full scale current limit the capacitor connected to $C_{OL1}/C_{OL2}$ begins to change. When the voltage across $C_{OL1}/C_{OL2}$ rises above 1.32V the output is immediately shut off. When ONx is deasserted or when the load current is above 15% of full scale current limit then this pin is held to $V_{EE}$ . Tying this pin to $V_{EE}$ will disable this function. |  |  |  |  |

| 17,14      | CGATE1/CGATE2   | Noise filtering capacitors for the gates of the main output MOSFETs.<br>Typically in the range of 1000pF ~ 4700pF.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 15         | VDDL            | $V_{DDL}$ provides the ground reference for the logic-compatible FAULT# and ON signals, while accommodating $\pm 8$ volts of ground differential between the controlling logic and the power ground (V_{DDA}) of the MIC2596/2597. If no differential voltage capability is required between V_{DDA} and V_{DDL}, these two pins should be tied together at the part.                                                                        |  |  |  |  |

| 13, 18     | N/C             | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

## **Absolute Maximum Ratings**

| (All voltages are referred to $V_{EE}$ ) | (Note 1)           |

|------------------------------------------|--------------------|

| Supply Voltage ( $V_{DDA}$ to $V_{EE}$ ) | –0.3V to 80V       |

| Supply Voltage ( $V_{DDL}$ to $V_{EE}$ ) | –0.3V to 80V       |

| V <sub>CLAMP</sub> pin (Note 2)          | –0.3V to 5.5V      |

| ON, FAULT# pins (Note 2)                 | –0.3V to 5.5V      |

| Junction Temperature                     | Internally Limited |

| ESD (Human Body Model)                   | [tbd]              |

| ESD (Machine Model)                      | [tbd]              |

## **Operating Ratings**

## **Electrical Characteristics**

| $V_{DDA} = V_{DDA}$ | $V_{\text{DDL}} = 40 \text{V},$ | $V_{EE} = 0V,$ | $V_{CLAMP} = 1$ | V <sub>DD</sub> + 3 | 3.3V, R <sub>LIMIT1</sub> | = R <sub>LIMIT2</sub> = 20 | )k , T <sub>A</sub> | = 25°C unless otherwise noted. |

|---------------------|---------------------------------|----------------|-----------------|---------------------|---------------------------|----------------------------|---------------------|--------------------------------|

|---------------------|---------------------------------|----------------|-----------------|---------------------|---------------------------|----------------------------|---------------------|--------------------------------|

| Symbol                | Parameter                                                                             | Condition                                                                                          | Min  | Тур   | Max  | Units |

|-----------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------|-------|------|-------|

| I <sub>DD</sub>       | Supply Current                                                                        | $V_{DDA} = V_{DDL} = 70V$ , Both outputs on or off<br>-40°C to 85°C                                |      | 3.3   | 5.0  | mA    |

| UVLO                  | Undervoltage Lockout threshold                                                        | V <sub>IN</sub> rising                                                                             | 11.5 |       | 12.5 | V     |

|                       | Undervoltage Lockout hysteresis                                                       | V <sub>IN</sub> falling                                                                            |      | -0.35 |      | V     |

| I <sub>CLAMP</sub>    | CLAMP pin supply current                                                              | FAULT#1 and FAULT#2 are high<br>V <sub>CLAMP</sub> = 5.25V                                         |      | 190   |      | μA    |

| V <sub>OL</sub>       | FAULT#[1/2] output low voltage<br>(Note 2)                                            | I <sub>OL</sub> = 250μA                                                                            | -0.3 | -0.18 | 0.4  | V     |

| R <sub>DSON</sub>     | On-Resistance (Each Switch)                                                           | $T_J = 25^{\circ}C$                                                                                |      | 1.5   | 2.0  | Ω     |

|                       | On-Resistance (Each Switch)                                                           | $T_J = 85^{\circ}C$                                                                                |      | 1.9   | 2.5  | Ω     |

| CLF                   | Current Limit Factor (Notes 4, 6)                                                     | $R_{LIMIT1} = R_{LIMIT2} = 40k$                                                                    | 1700 | 2000  | 2300 | Α•Ω   |

| I <sub>OFF</sub>      | Off-state Output leakage current                                                      | Switch is off, $T_J = 25^{\circ}C$<br>V <sub>OUT</sub> = V <sub>DDA</sub> = V <sub>DDL</sub> = 70V |      |       | 2    | μA    |

|                       | Off-state Output leakage current                                                      | Switch is off, $T_J = 85^{\circ}C$<br>V <sub>OUT</sub> = V <sub>DDA</sub> = V <sub>DDL</sub> = 70V |      |       | 5    | μA    |

| I <sub>TIMER</sub>    | Overcurrent Timer pull-down current                                                   |                                                                                                    | 1.1  | 1.9   | 2.7  | μA    |

|                       | Overcurrent Timer charge current                                                      |                                                                                                    | -42  | -72   | -103 | μA    |

| I <sub>OLDTH</sub>    | Open Load Detect threshold                                                            | I <sub>OUT</sub> decreasing                                                                        | 6    | 9     | 12   | %     |

|                       | (percent of full-scale output current)<br>(Notes 5, 6)                                | I <sub>OUT</sub> increasing                                                                        | 8    | 12    | 16   | %     |

| IOLDHYS               | Open Load Detect hysteresis<br>(percent of full-scale output current)                 |                                                                                                    |      | 3     |      | %     |

| V <sub>THHI</sub>     | Overload Timer Capacitor<br>high-going threshold voltage                              |                                                                                                    | 1.12 | 1.32  | 1.52 | V     |

| V <sub>THLO</sub>     | Overload Timer low -going threshold<br>voltage for auto-restart (MIC2596)<br>(Note 6) |                                                                                                    | 0.21 | 0.24  | 0.27 | V     |

| I <sub>GATE</sub>     | C <sub>GATE</sub> Capacitor charge current                                            | During turn-on                                                                                     |      | -79   |      | μA    |

| V <sub>COL</sub>      | Open Load Detect Timer high-going threshold voltage                                   |                                                                                                    | 1.12 | 1.32  | 1.52 | V     |

| I <sub>COL</sub>      | Open-Load Detect Timer capacitor charge current                                       |                                                                                                    | -10  | -17   | -24  | μA    |

| V <sub>FBU</sub>      | Output voltage foldback threshold                                                     | Upper threshold                                                                                    | 25   | 31    | 37   | V     |

| V <sub>FBL</sub>      |                                                                                       | Lower threshold                                                                                    | 10   | 13    | 16   | V     |

| I <sub>FOLDBACK</sub> | Foldback output current limit                                                         | V <sub>OUT</sub> – V <sub>EE</sub> > V <sub>FBU</sub> , % of full scale<br>current limit           | 12   | 20    | 28   | %     |

| Symbol                 | Parameter                                   | Condition                                      | Min | Тур   | Max | Units |

|------------------------|---------------------------------------------|------------------------------------------------|-----|-------|-----|-------|

| V <sub>IL</sub>        | ON Pin Low threshold Voltage                | -40°C to 85°C                                  |     |       | 0.8 | V     |

| I <sub>IL</sub>        | ON Pin input current                        | V <sub>ON</sub> = V <sub>CLAMP</sub>           |     |       | 150 | μΑ    |

| V <sub>IH</sub>        | ON Pin High threshold voltage               | -40°C to 85°C                                  | 2.0 |       |     | V     |

| T <sub>PROTECT</sub>   | Thermal self-protection points              | T <sub>J</sub> increasing (turn-off)           |     | 145   |     | °C    |

|                        |                                             | T <sub>J</sub> decreasing (turn-on)            |     | 135   |     | °C    |

| AC Paramet             | ers                                         | ·                                              |     |       |     | •     |

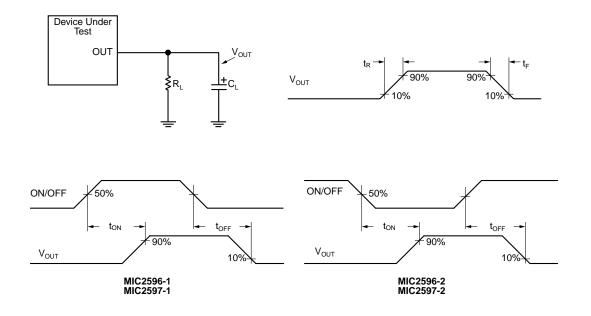

| t <sub>ON</sub>        | Turn-on time                                | $C_L = 1\mu F, R_L = 1k\Omega, C_{GATE} = 1nF$ |     | [tbd] |     | ms    |

| t <sub>OFF</sub>       | Turn-off time                               | $C_L = 1\mu F, R_L = 1k\Omega, C_{GATE} = 1nF$ |     | [tbd] |     | ms    |

| t <sub>R</sub>         | Rise-time                                   | $C_L = 1\mu F, R_L = 1k\Omega, C_{GATE} = 1nF$ |     | [tbd] |     | ms    |

| t <sub>F</sub>         | Fall-time                                   | $C_L = 1\mu F, R_L = 1k\Omega, C_{GATE} = 1nF$ |     | [tbd] |     | ms    |

| t <sub>oc</sub>        | Current limit response time                 | C <sub>GATE</sub> ≤ 1nF                        |     | 4     |     | μs    |

| t <sub>OFF(UVLO)</sub> | Undervoltage to OUT1/OUT2 off response time | $C_L = 1\mu F, R_L = 1k\Omega, C_{GATE} = 1nF$ |     | [tbd] |     | μs    |

Notes:

Note 1: Absolute Maximum Ratings are those ratings beyond which a part may be permanently damaged. Functionality is not guaranteed when a part is operated at its Absolute Maximum Ratings.

Note 2: Relative to V<sub>DDL</sub>.

Note 3: The exposed pad of the TSE package must be connected to  $V_{EE}$  of the part, or be electrically isolated.

Note 4: The current limit threshold is defined by the current limit factor divided by R<sub>LIMIT</sub>, the resistor connected to the I<sub>LIMIT1</sub>/I<sub>LIMIT2</sub> pins.

Note 5: Open Load Detect is not guaranteed to function for programmed maximum output currents <[tbd]mA

Note 6: Final production value TBD.

## **Timing Diagrams**

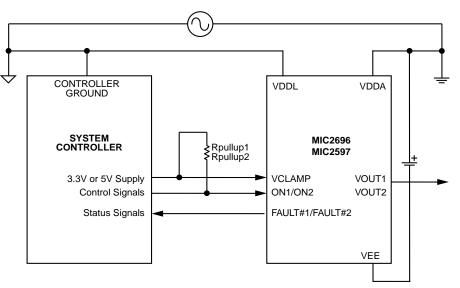

Figure 1. Use of V<sub>DDA</sub> and V<sub>DDL</sub> to Mitigate Ground Noise Effects

## **Functional Description**

#### **Hot Swap Insertion**

When circuit boards are inserted into systems with live power supplies, high inrush currents can result due to the charging of bulk capacitance that resides across the circuit board's supply pins. This inrush current, although transient in nature, can be of significant amplitude. Such current spikes can cause supply voltages to go out of regulation, resulting in system crashes. Additionally, the high rates of di/dt may do permanent damage to electronic components and/or assemblies.

The MIC2596 family of parts is designed to address these issues by limiting the inrush current which a PC board or other load can draw during a hot-swap event. In addition to this inrush current control, the MIC2596/MIC2597 provide output current limiting and supervisory functions to ensure robust protection for both the host system and the circuit board.

#### $\rm V_{DDA}$ and $\rm V_{DDL}$

In some systems, considerable ground differentials can occur between the physical plant monitor and the actual power control circuitry. An example of this would be in a system spanning several racks of equipment, with a centralized CPU watching over the hot-swap functions. In order to alleviate the need for optical isolators or similar devices when hot-swap parts are used in such a system, the MIC2596/MIC2597 have separate grounds for their on-chip power-related functions and their digital interface pins (ON1, ON2, FAULT1#, FAULT2#). The unique architecture of these parts allows voltage differentials of  $\pm 8$  volts to exist between V<sub>DDA</sub> (the "analog" ground) and  $V_{\mbox{\scriptsize DDL}}$  (the "logic" ground), without disturbing device performance.

In distributed systems,  $V_{DDA}$  should be connected to the local return of the power which the MIC2596/MIC2597 is controlling, while  $V_{DDL}$  should be separately connected to the monitor and control logic's ground. See Figure 1. If the capability to tolerate voltage differentials between  $V_{DDA}$  and  $V_{DDL}$  is not required, the two grounds should be tied together at the chip.

#### Start-Up Cycle

Referring to the Typical Applications Circuit, when a channel's ON pin is asserted the respective MIC2596/MIC2597 output is enabled. To minimize inrush current transients the output current is regulated to ensure that it does not exceed the value programmed by the resistor R1(R2) connected to the  $I_{\rm I,MIT}$  pin.

#### **Circuit Breaker Function**

The MIC2596 and MIC2597 act as electronic circuit breakers to protect loads, connectors, power supplies, and other system components against faults such as short circuits. The circuit breaker function trips upon overcurrent, open-load or thermal shutdown conditions. The FAULT# output is asserted (taken low) when the circuit breaker is tripped. The timer capacitor C2 (C3) is normally pulled low by a small current source. However, whenever the current limit threshold is exceeded C2 is charged by a much stronger current source. If an overcurrent condition exists for a long enough time to allow the voltage at the  $C_{TIMFR}$  pin to cross the

threshold  $V_{THHI}$ , the circuit beaker is tripped and the output is immediately turned off. This time-out period t<sub>FIT</sub> prevents the circuit breaker from erroneously tripping due to inrush currents during start-up or other transient currents caused by normal system operation.

The MIC2596 circuit breaker has an automatic-reset function. After the circuit breaker trips a new start-up cycle is initiated. If the fault still exists C2 (C3) will again charge up to V<sub>THHI</sub> and trip the circuit breaker. C2 will then be discharged, and when the voltage across C2 goes below  $V_{THIO}$ another start cycle is initiated. This will continue until the fault is removed or the channel is turned off. In the MIC2597 the circuit breaker is only reset by either toggling the ON pin or cycling input power. The MIC2597 will be enabled to start up only if the voltage across C<sub>TIMER</sub> is below V<sub>THLO</sub>.

#### Foldback Current Limiting

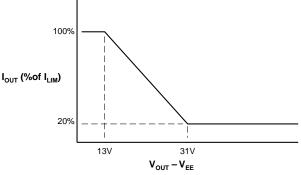

During short circuits or excessive loads the MIC2596 and MIC2597 employ foldback current limiting. When the differential from  $V_{EE}$  to  $V_{OUT}$  reaches -13V, the output current starts to fold back. When  $(V_{EE} - V_{OUT})$  reaches -31V, the output current will be limited to approximately 20% of its full scale value. Figure 2 illustrates the foldback function.

Micrel

**Figure 2. Foldback Characteristics**

#### **Fault Status Indication**

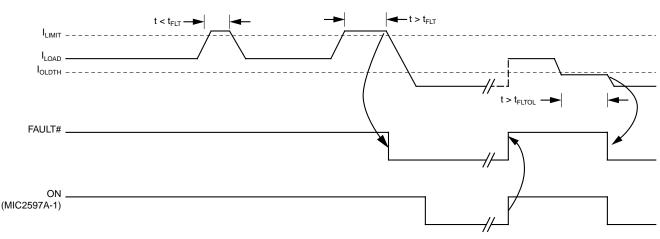

The MIC2596 and MIC2597 will assert the FAULT# output whenever their circuit breaker function is activated by an overcurrent condition. A fault will also be indicated if an openload or thermal shutdown condition is detected. Figure 3 shows FAULT# timing scenarios.

Figure 3. MIC2597 Fault Timing

## **Application Information**

#### **Thermal Shutdown and Power Dissipation**

Thermal shutdown protection is employed to protect the internal power MOSFETs from damage. Whenever the junction temperature  $T_J$  of the channel in current limit exceeds 145°C the output is immediately shut off without affecting the other channel. A channel will automatically turn on again when its  $T_J$  falls below 135°C. The junction temperature is related to the internal power dissipation of the MIC2596 (MIC2597). The equation for junction temperature is:

$T_J = [(\theta_{JA} \cdot P_D) + T_A]$  where:

T<sub>J</sub> is the junction temperature,

$P_D$  is the total power dissipation of the part, and

T<sub>A</sub> is the ambient temperature.

$\mathsf{P}_{\mathsf{D}}$  is determined by adding the power dissipated by each MOSFET to the power dissipated by the internal circuitry ( $\mathsf{P}_{\mathsf{CHIP}}$ ). The equation for  $\mathsf{P}_{\mathsf{D}}$  is thus:

$P_{D} = P_{CHIP} + P_{FET1} + P_{FET2}$ = (V<sub>EE</sub> x I<sub>EE</sub>) + [(I<sub>1</sub><sup>2</sup>) x R<sub>DS(ON)1</sub>] + [(I<sub>2</sub><sup>2</sup>) x R<sub>DS(ON)2</sub>] where I<sub>1</sub> and I<sub>2</sub> are the continuous output currents of channels 1 and 2.

For example, to compute the maximum continuous output current per channel of the TSSOP package at  $V_{EE} = -48V$ ,  $T_A = 70^{\circ}$ C, and  $T_{.I(CONTINUOUS)} = 125^{\circ}$ C:

$$R_{\theta(J-A)} = 90^{\circ}C/W$$

$$P_{D(MAX)} = (125^{\circ}C - 70^{\circ}C)/(90^{\circ}C/W) = 0.611W$$

$$0.611W = (-48V \times -5mA) + (2 \times I_{MAX}^2 \times 2.5\Omega)$$

$$0.371W = 2 \times 2.5\Omega \times I_{MAX}^2$$

$$0.371W/(2 \times 2.5\Omega) = I_{MAX}^2 = 0.0742 \text{ A}^2$$

$$I_{MAX} = 272\text{mA per channel}$$

Similarly, for the TSE package, at  $T_A = 85^{\circ}C$  and  $T_{J(CONTINUOUS)} = 125^{\circ}C$ :

$$\begin{split} \mathsf{R}_{\theta(J\text{-}A)} &= 38^\circ\text{C/W} \\ \mathsf{P}_{\mathsf{D}(\mathsf{MAX})} &= (125^\circ\text{C} - 85^\circ\text{C})/(38^\circ\text{C/W}) = 1.05\text{W} \\ 1.05 \text{ W} &= (-48\text{V x} - 5\text{mA}) + (2 \times \text{I}_{\mathsf{MAX}}^2 \times 2.5\Omega) \\ 0.81\text{W} &= 2 \times 2.5\Omega \times \text{I}_{\mathsf{MAX}}^2 \\ 0.81\text{W}/(2 \times 2.5\Omega) &= \text{I}_{\mathsf{MAX}}^2 = 0.162 \text{ A}^2 \\ \text{I}_{\mathsf{MAX}} &= 402\text{mA per channel} \end{split}$$

Note that in each case the assumption has been made that the load currents will be the same on both channels.

#### **External Components**

A small number of passive components are used for each channel of the MIC2596/MIC2597 to program such values as maximum DC output current and the short circuit "trip" interval. Calculating values for these parts is a straightforward exercise, once the nomenclature for and effect of each such part is understood. This section addresses each programmable pin by showing a sample calculation for that pin.

#### R<sub>LIMIT</sub>

A resistor from I<sub>LIMIT</sub> to V<sub>EE</sub> sets the maximum DC operating current of the channel. The formula for calculating this resistance is R<sub>LIMIT(NOMINAL)</sub> = (1A·2000 $\Omega$ )/I<sub>LIMIT</sub>. As an

example, if the maximum DC current from one channel of an MIC2596 was to be 0.15A, the nominal value of R<sub>LIMIT</sub> for that channel would be  $(1A \cdot 2000\Omega)/0.15A = 13.3k\Omega$ . It is usually necessary, however, to allow for device tolerances: using a 13.3kΩ resistor and the minimum Data Sheet value Current Limit Factor of (1A·1700Ω)/R<sub>I IMIT</sub> could restrict the part to delivering only 127mA. Therefore, it is necessary to use  $R_{LIMIT} = (1A \cdot 1700\Omega)/I_{LIMIT}$  to find  $R_{LIMIT}$ 's minimum value:  $1700/0.15A = 11.3k\Omega$ . This revised value should then be tested against the other extreme of the IC's Data Sheet tolerance. 11.3k $\Omega$  could program a steady-state DC current as high as  $(1A.2300\Omega)/11.3k\Omega = 203mA$  maximum. The system must be designed to accommodate this maximum current, or R<sub>LIMIT</sub> can be made adjustable over the range necessary to maintain a precise 150mA DC current limit  $(11.3k\Omega - 15.3k\Omega)$ . In order to minimize error budget issues, the use of a 1% tolerance resistor for R<sub>LIMIT</sub> is generally recommended.

#### CTIMER

A capacitor from  $C_{TIMER}$  to  $V_{EE}$  sets the length of time for which an overcurrent fault is allowed to exist on a channel before the channel goes into shutdown.  $C_{TIMER}$  is normally pulled down to  $V_{EE}$  by a small current (1.9µA nominal). During an overcurrent condition, the pulldown current is replaced by a charging current of 72µA nominal. The output will be disabled once the voltage on  $C_{TIMER}$  becomes 1.32V greater than  $V_{EE}$ . Given these numbers, it's easy to program the time an MIC2597 will tolerate an output overload before "tripping" and shutting its output off, using the formula  $C_{TIMER}$ = (72µA·T<sub>OL</sub>/1.32V). For example, if it's desired to allow 50msec for the load capacitance to charge up before the MIC2597 declares a "fault," then  $C_{TIMER}$  = (72µA·50msec/ 1.32V) = 2.7µF.

For the MIC2596, there is a slight modification to the above formula, due to the MIC2596's auto-retry feature. When an overcurrent condition occurs, C<sub>TIMER</sub> will (as with the MIC2597) charge at a 72µA rate towards 1.32V. Once that threshold is reached, the output will be turned off. However, instead of being latched off as with the MIC2597, it will turn on again when the voltage across  $C_{TIMFR}$  is discharged back to 0.24V by the 1.9µA internal pulldown. The first fault timeout period following power-on will therefore be  $T_{OL} = (C_{TIMER} \cdot 1.32V/$ 72 $\mu$ A), but the following retry intervals will be of duration T<sub>OI</sub>  $= [C_{TIMFR} \cdot (1.3V - 0.24V)/72\mu A] = (C_{TIMFR} \cdot 1.06V/72\mu A).$  Rearranging, we get:  $C_{TIMER} = (72\mu A \cdot T_{OL} / 1.06V)$ . Again using 50msec as an example for the desired fault timeout, this gives  $C_{TIMER} = (72\mu A \cdot 50 \text{ msec}/1.06 \text{ V}) = 3.4\mu\text{F}$ . In this case,  $3.3\mu\text{F}$ would be a good choice for  $C_{TIMER}$ . The maximum voltage to which  $C_{TIMER}$  will charge is less than 2V, so a 4.7V voltage rating on the capacitor provides ample safety margin.

Note that, for the MIC2596, the ratio of  $C_{\text{TIMER}}$  charge and discharge currents are always 38:1. This means that in an overload fault condition, the part will attempt to restart the load with a duty cycle of approximately 2.5%, which is low enough to protect the IC and the system, yet high enough to prevent undue restart delays.

## COL

One of the special functions of the MIC2596 family of parts is the ability to detect not only overload faults, but also undercurrent (open-load) faults. The time for which a channel's output must see a load below a minimum current level (which is a preset percentage of ILIMIT - see the Data Sheet Electrical Tables) is set by C<sub>OI</sub>. When an undercurrent condition is detected, C<sub>OI</sub> is charged from 0V relative to V<sub>FF</sub> towards a threshold voltage of 1.32V above  $V_{EE}$  by a current of 17µA (nominal). This gives the formula  $C_{OL} = (17\mu A \cdot T_{OL}/1.32V)$ . For example, if a no-load detection period of 75msec is desired,  $C_{OI}$  is found to be 0.97µF. 1µF is the closest standard value. Once the output current goes above the minimum load current, COL is discharged to VEE. The maximum voltage to which  $\dot{C}_{OI}$  will charge is less than 2V, so a 4.7V voltage rating on the capacitor provides ample safety margin.

It is important to note that neither the MIC2596 nor the MIC2597 will attempt an "auto-retry" upon detecting an openload condition. If either of these parts shuts one or both of its output off following such a condition, the affected output(s) can only be turned on again by turning the channel(s) off and then back on, or by cycling the power to the IC. If the open load detection capability is not needed for a given channel, it can be defeated by tying the  $C_{OL}$  pin for that channel to  $V_{EE}$ .

#### C<sub>GATE</sub>

This pin is a direct connection to the gate of each channel's internal power MOSFET. Typically, it is used to connect a capacitor in the range of 1000pF to 4700pF between the MOSFET gate and  $V_{EE}$ , to augment the noise immunity of the channel. This especially helps with regard to dv/dt appearing on the channel's output, which could otherwise couple through the drain-gate capacitance to the MOSFET's input.

As the internal MOSFET is an N-channel device in the negative leg of the channel's power path, the negative terminal of  $C_{GATE}$  should connect to  $V_{EE}$ , and its positive terminal to the IC's  $C_{GATE}$  pin. A voltage rating of 15V is well suited to the approximately 10V which will appear on  $C_{GATE}$  when the internal MOSFET is fully enhanced.

**Stand Alone Hot Swap Application**

## **Package Information**

#### MICREL INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 2000 Micrel Incorporated